## DESIGN AND TEST OF AN EVENT DETECTOR AND LOCATOR FOR THE REFLECTOACTIVE™ SEALS SYSTEM

Brad J. Stinson Oak Ridge National Laboratory Bldg. 3606 MS 6003, P.O. Box 2008 Oak Ridge, TN 37831 865/241-6757 FAX 865/574-4529

#### ABSTRACT

The purpose of this work was to research, design, develop and test a novel instrument for detecting fiber optic loop continuity and spatially locating fiber optic breaches. The work is for an active seal system called ReflectoActive<sup>™</sup> Seals whose purpose is to provide real time container tamper indication.

A Field Programmable Gate Array was used to implement a loop continuity detector and a spatial breach locator based on a high acquisition speed single photon counting optical time domain reflectometer. Communication and other control features were added in order to create a usable instrument that met defined requirements. A host graphical user interface was developed to illustrate system use and performance.

The resulting device meets performance specifications by exhibiting a dynamic range of 27dB and a spatial resolution of 1.5 ft. The communication scheme used expands installation options and allows the device to communicate to a central host via existing Local Area Networks and/or the Internet.

## **Table of Contents**

|                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 2.0 Background                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                                                          |

| 2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 2.2 Previous Work                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

| 2.2.1 OTDR Only Approach                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                            |

| 2.2.2 Analog Immediate Detection Unit and Tektronix OTDR                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                            |

| 2.2.3 Digital Immediate Detection Unit with Tektronix OTDR                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

| 2.3 Optical Time Domain Reflectometer Review                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| 2.3.1 Design of a basic OTDR                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| 2.3.1 OTDR Dead Zones                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 2.3.2 Analog OTDR Resolution Limits                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| 2.3.3 OTDR Ghosting                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| 2.3.4 Photon Counting OTDR                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| 3.0 System Design Concepts                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| 3.2 Simple Deployment                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 3.3 Common Deployment                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 3.4 Event Detector and Locator Theory of Operation                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

| 3.4.1 EDL in the Event Detection Mode                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 3.4.2 EDL in the Event Location Mode                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| 4.0 Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                     | 24                                                                                                                         |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| 4.2 Power Circuitry                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| 4.2 Power Circuitry<br>4.3 FPGA and Support Circuitry                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| 4.3 FPGA and Support Circuitry                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |

| <ul><li>4.3 FPGA and Support Circuitry</li><li>4.4 Low Cost Picosecond Laser Driver</li></ul>                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| <ul><li>4.3 FPGA and Support Circuitry</li><li>4.4 Low Cost Picosecond Laser Driver</li><li>4.5 Control and Communication Module</li></ul>                                                                                                                                                                                                                                                                              | 25<br>25<br>27<br>32                                                                                                       |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>25<br>27<br>32<br>32<br>35                                                                                           |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>25<br>27<br>32<br>32<br>35<br>37                                                                                     |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>25<br>27<br>32<br>35<br>35<br>37<br>37                                                                               |

| <ul> <li>4.3 FPGA and Support Circuitry</li> <li>4.4 Low Cost Picosecond Laser Driver</li> <li>4.5 Control and Communication Module</li> <li>4.6 Alarm Circuitry</li> <li>4.7 Optical Components</li> <li>4.7.1 Laser Diode</li> <li>4.7.2 1x2 Coupler</li> </ul>                                                                                                                                                       | 25<br>25<br>27<br>32<br>35<br>37<br>37<br>37                                                                               |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>25<br>27<br>32<br>35<br>37<br>37<br>37<br>37<br>38                                                                   |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>25<br>27<br>32<br>35<br>37<br>37<br>37<br>37<br>38<br>38                                                             |

| <ul> <li>4.3 FPGA and Support Circuitry</li> <li>4.4 Low Cost Picosecond Laser Driver</li> <li>4.5 Control and Communication Module</li> <li>4.6 Alarm Circuitry</li> <li>4.7 Optical Components</li> <li>4.7.1 Laser Diode</li> <li>4.7.2 1x2 Coupler</li> <li>4.7.3 Optical Switches</li> <li>4.7.4 Dicon Fiber Optic Variable Attenuator</li> <li>4.8 Perkin-Elmer Single Photon Avalanche Photo Detector</li> </ul> | 25<br>25<br>27<br>32<br>35<br>37<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>39                                           |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>25<br>27<br>32<br>35<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>39<br>40                                           |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>25<br>27<br>32<br>35<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>38<br>38<br>40<br>40                               |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>27<br>32<br>35<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>39<br>40<br>41<br>42                                     |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>27<br>32<br>35<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>38<br>40<br>40<br>41<br>42<br>42                         |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>27<br>32<br>32<br>35<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>39<br>40<br>41<br>41<br><b>42</b><br>42<br>42      |

| <ul> <li>4.3 FPGA and Support Circuitry</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 25<br>27<br>32<br>35<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>38<br>39<br>40<br>41<br>41<br>41<br>42<br>42<br>42<br>44 |

| 5.4 Photon Counting OTDR in VHDL and Block Diagram      |    |

|---------------------------------------------------------|----|

| 5.4.1 v-OTDR Signal Generation                          |    |

| 5.4.2 v-OTDR Control                                    |    |

| 5.4.2 v-OTDR High Speed Sampling Using Phase Offset PLL |    |

| 5.4.3 v-OTDR Waveform Transfer                          |    |

| 5.5 Communication and System Control in Dynamic C       |    |

| 5.5.2 Network Communication                             |    |

| 5.5.1 Communication with FPGA                           |    |

| 5.5.3 Optical Switch Control                            |    |

| 5.5.4 Attenuator Control and Calibration                |    |

| 5.5.5 Alarm Interface                                   |    |

| 5.5.6 Tamper Input                                      |    |

| 5.5.7 Display Control                                   | 74 |

| 5.6 Windows Graphical User Interface in Microsoft C#    |    |

| 5.6.1 EDL Status Display and Control                    |    |

| 5.6.2 Event Logging                                     | 77 |

| 5.6.3 Item Addition and Removal                         |    |

| 5.6.4 Illustration of Maintaining User Accountability   |    |

| 5.6.5 v-OTDR Waveform Display and Characterization      |    |

| 5.6.6 Breach Location Algorithm                         |    |

| 6.0 Design Results and Performance                      |    |

| 6.1 Introduction                                        |    |

| 6.2 Event Detector Performance                          |    |

| 6.3 Event Locator (v-OTDR) Performance                  |    |

| 7.0 Conclusions                                         | 88 |

| 7.1 Contributions                                       |    |

| 7.2 Future Work and Research                            |    |

|                                                         |    |

| REFERENCES                                              |    |

|                                                         |    |

# List of Figures

| Figure 1: Successive OTDR Scan Comparison                    | 5  |

|--------------------------------------------------------------|----|

| Figure 2: Analog IDU with Tektronix OTDR                     | 6  |

| Figure 3: First OTDR by Barnoski and Jensen                  | 9  |

| Figure 4: Histogram Based on Table 1                         | 13 |

| Figure 5: Single Loop RAS Deployment                         | 17 |

| Figure 6: Typical RAS Deployment                             | 18 |

| Figure 7: Typical RAS Facility Implementation                | 19 |

| Figure 8: EDL Block Diagram in Event Detection Mode          | 22 |

| Figure 9: EDL Block Diagram in Event Location Mode           | 23 |

| Figure 10: EDL Circuitry                                     | 24 |

| Figure 11: ECL Based Core of Picosecond Diode Driver         | 29 |

| Figure 12: Input Stage of Picosecond Diode Driver            | 31 |

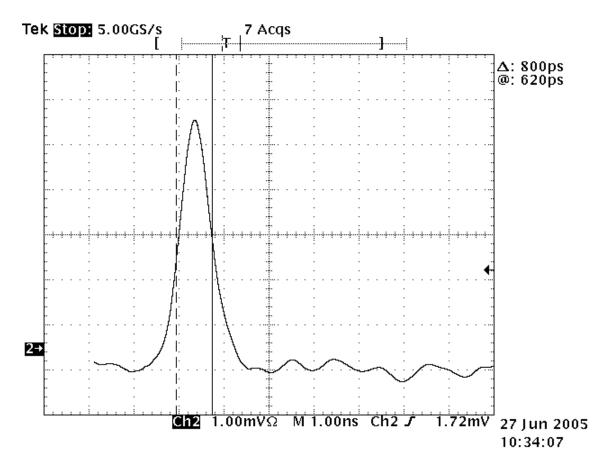

| Figure 13: Picosecond Driver Delayed Pulse Response          | 31 |

| Figure 14: Picosecond Driver Optical Output Pulse            | 33 |

| Figure 15: Rabbit RCM3360 Core Module                        | 33 |

| Figure 16: Alarm Interface Circuitry                         | 36 |

| Figure 17: EDL Light Emitting Diode Circuit                  | 36 |

| Figure 18: 2x2 Optical Switch in Reverse Mode                | 38 |

| Figure 19: SPCM-AQR Single Photon Counter Optical Efficiency | 40 |

| Figure 20: Event Detector and Locator Enclosure              | 41 |

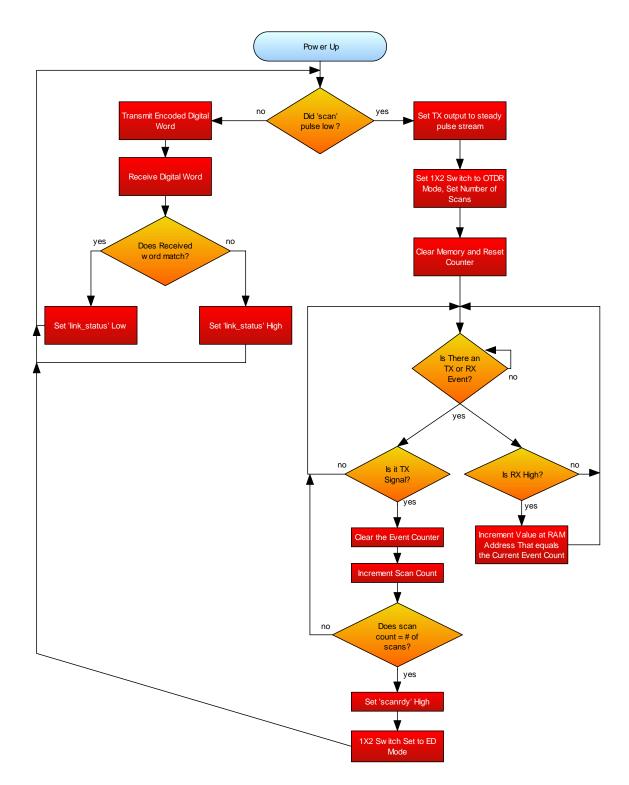

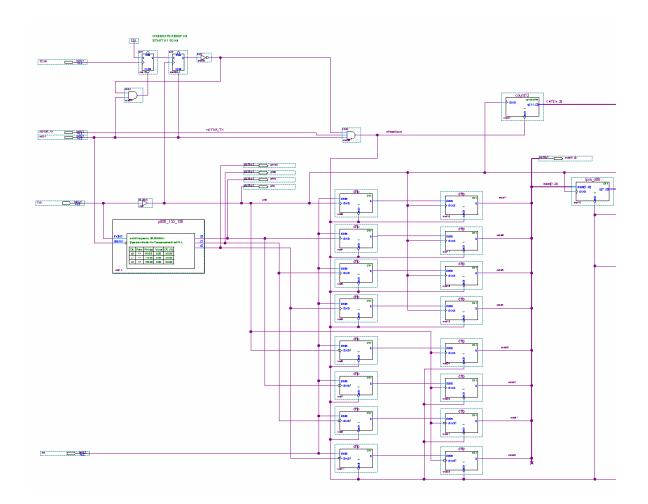

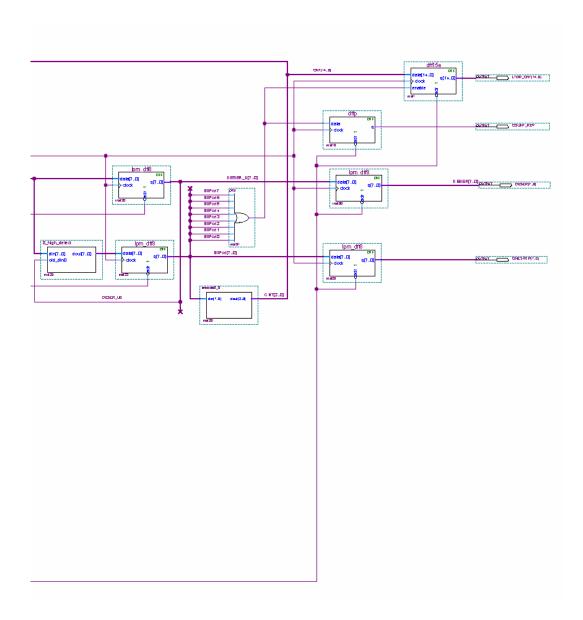

| Figure 21: FPGA Software Flowchart                           | 43 |

| Figure 22: VHDL Mode Control Process                         | 45 |

| Figure 23: Event Detection Signal Transmission VHDL          |    |

|--------------------------------------------------------------|----|

| Figure 24: Event Detection Signal Reception VHDL             | 49 |

| Figure 25: v-OTDR Control State Machine in VHDL              | 53 |

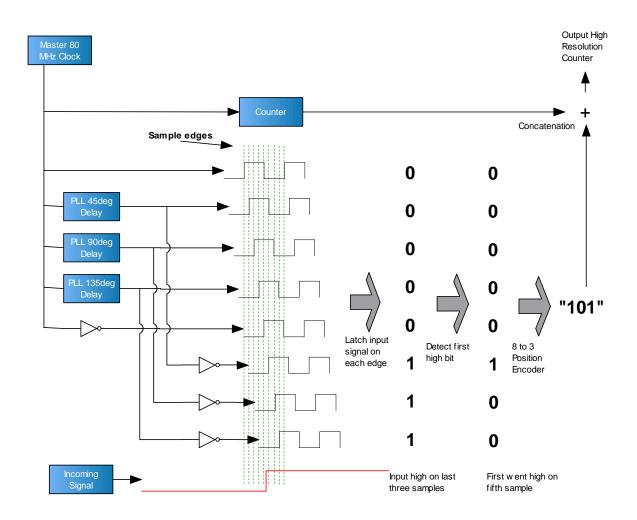

| Figure 26: High Speed Sampling in VHDL with Phase Offset PLL |    |

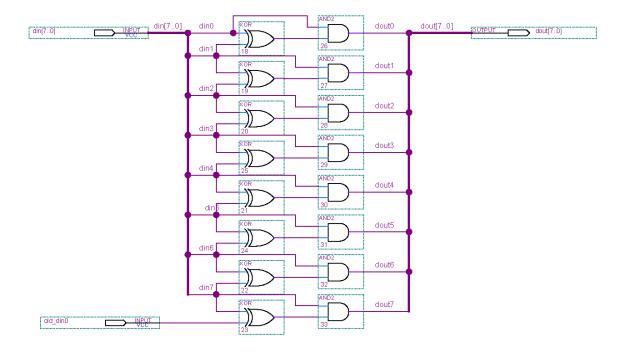

| Figure 27: Altera Block Diagram of High Bit Detector         | 60 |

| Figure 28: Phase Delay Based High Speed Sampler              | 61 |

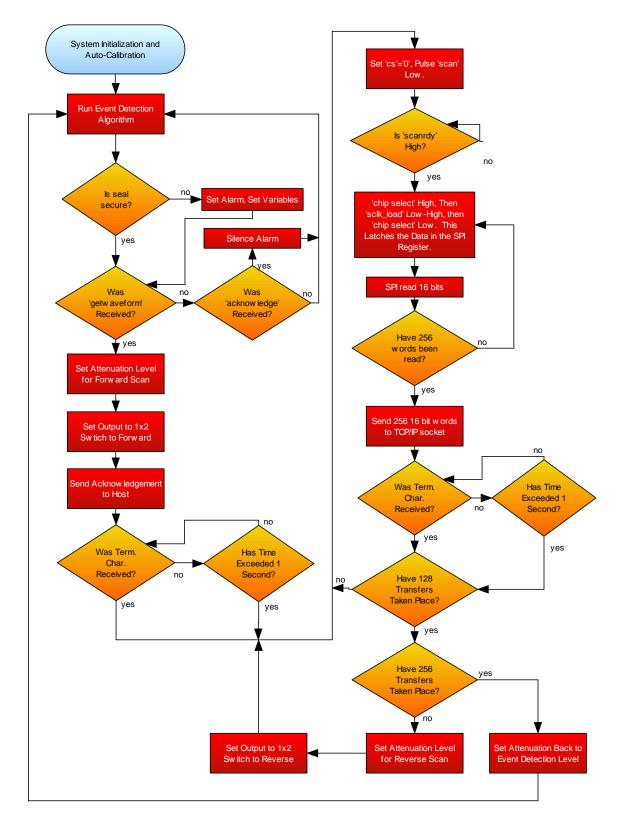

| Figure 29: RCM3360 Firmware Flowchart                        | 65 |

| Figure 30: EDL Main Page in HTML                             | 67 |

| Figure 31: EDL Administrator Tools HTML Page                 | 68 |

| Figure 32: GetStatus.cgi Returned XML Document               | 69 |

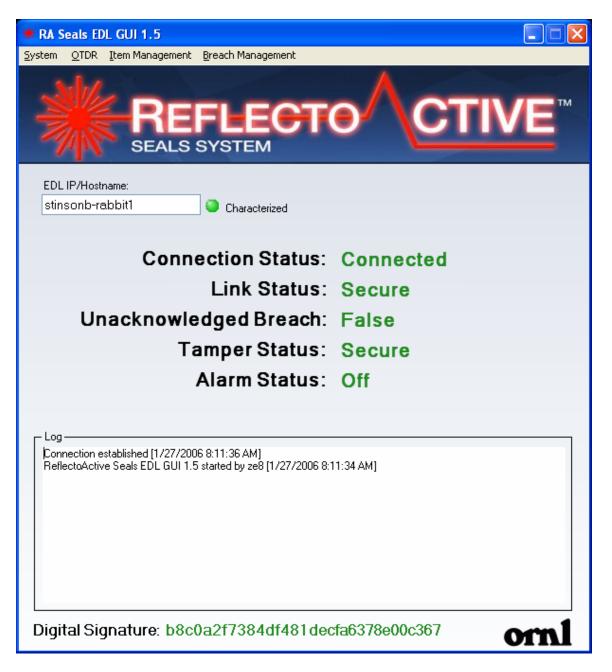

| Figure 33: RAS GUI Main Screen                               |    |

| Figure 34: RAS GUI User Authentication                       |    |

| Figure 35: RAS GUI v-OTDR Screen                             | 79 |

| Figure 36: v-OTDR Waveform Illustrating Breach Location      |    |

| Figure 37: v-OTDR Spatial Resolution Limit Test              | 85 |

## List of Abbreviations

| APD    | Avalanche Photodiode Detector                      |

|--------|----------------------------------------------------|

| CGI    | Common Gateway Interface                           |

| DIDU   | Digital Immediate Detection Unit                   |

| DPRAM  | Dual Port Random Access Memory                     |

| ECL    | Emitter Coupled Logic                              |

| EDL    | Event Detector and Locator                         |

| FPGA   | Field Programmable Gate Array                      |

| FWHM   | Full Width Half Maximum                            |

| GUI    | Graphical User Interface                           |

| HTML   | Hyper Text Markup Language                         |

| HTTP   | Hyper Text Transfer Protocol                       |

| IDU    | Immediate Detection Unit                           |

| LAN    | Local Area Network                                 |

| LCD    | Liquid Crystal Display                             |

| LED    | Light Emitting Diode                               |

| LFSR   | Linear Feedback Shift Register                     |

| OTDR   | Optical Time Domain Reflectometer                  |

| OTS    | Off The Shelf                                      |

| PECL   | Positive Emitter Coupled Logic                     |

| PLL    | Phase-Locked Loop                                  |

| RAM    | Random Access Memory                               |

| RAS    | ReflectoActive <sup>™</sup> Seals                  |

| RF     | Radio Frequency                                    |

| SNR    | Signal to Noise Ratio                              |

| SPAD   | Single Photon Avalanche photodiode<br>Detector     |

| SPI    | Serial Peripheral Interface                        |

| SRAM   | Static Random Access Memory                        |

| TCP/IP | Telecommunications Protocol /<br>Internet Protocol |

| TID    | Tamper Indicating Devices                          |

| TTL    | Transistor-Transistor Logic                        |

|        |                                                    |

| VHDL   | Very High Speed Integrate Circuit   |

|--------|-------------------------------------|

|        | Hardware Description Language       |

| XML    | eXtensible Markup Language          |

| v-OTDR | Single Photon Counting Optical Time |

|        | Domain Reflectometer                |

#### **1.0 Introduction**

In the mid 1990s a request was made for a material accountability system that could provide continuous near real-time container tamper indication. To meet the requirements, a system must use "active" seals affixed to containers in a manner such that opening or tampering with the lid of the container causes the seal to be broken. The requested systems replace or supplement passive tamper indicating devices (TIDs) that require manual visual inspection to determine their status. The systems must employ reusable seals, be low cost, low maintenance, easy to use, safe for sensitive processing areas and provide near real-time indication of which seal is broken or being tampered with.

The benefits of such systems include a dramatic improvement in the safeguarding and accountability of valuable assets. Because assets are monitored continuously, a tamper attempt is known immediately. This is in contrast to passive TIDs, where a tamper attempt remains unknown until the next physical inspection. In some cases, government agencies will approve an extension of the period between mandated physical inventories based on the use of continuous monitoring technology. Fewer physical inventories translate to reduced cost and in some cases reduced worker exposure to hazardous materials.

#### 2.0 Background

#### **2.1 Introduction**

Past active seal designs provide a very important foundation for this work. As such, it is worthwhile to consider the requirements, challenges and constraints faced during the early designs. The next few paragraphs will explain in more detail the requirements and constraints associated with an active seal system and why a fiber optic based approach was originally chosen.

The first and perhaps most important requirement is that the system be secure and reliable. From the beginning, a wireless system was out of the question due to security regulations, so some form of wired system is required. An electrical system is vulnerable to splicing and patching around the seal. An optical system is much more difficult to splice into (requires specialized tools and specialized skills). Even if a fiber optic cable could be spliced without a disruption of signal, the loss of light caused by a splice is detected easily by an OTDR. In contrast to considered electrical solutions, light propagating through a fiber can travel several kilometers without needing regeneration due to signal degradation. Finally, fiber optic components are widely used in the telecom industry and have been proven reliable.

Second only to security is cost. In order to reduce cost and design time, the system needs to use off-the-shelf components where possible. The fiber optic industry is quite mature and components such as fiber, connectors, transmitters, receivers, switches and multiplexers are becoming more available and more affordable every day.

The next requirement is that the system be adaptable to a wide range of facilities and storage containers. The design needs to be able to form a seal on drum rings as well as other proprietary storage containers. The design needs to be capable of monitoring anywhere from a few dozen items up to thousands of items. Fiber optic connectors are available in a wide variety and are easily adapted to form seals on different types of enclosures or containers. The ST connector is employed because it is easy to use but unlikely to be accidentally unplugged. The ST connector is a keyed-bayonet style connector suitable for multimode or singlemode connections. Multimode fiber was used because of an increased alignment tolerance (due to a larger fiber core) and because multimode connections generate larger Fresnel reflections.

The final requirement is that the system be robust enough to withstand a shop floor environment. The fiber optic cable is Kevlar reinforced and has proven to be quite durable. When the system is closed (secure) it is insensitive to dust and other contaminants. In addition, fiber optics are insensitive to temperature variance, work well in radio frequency (RF) noisy areas and are safe for OSHA class I, II and III facilities [1].

#### **2.2 Previous Work**

The initial design of a fiber optic seal system began in the mid 1990s. The first design (as well as all future designs) was given the name ReflectoActive<sup>™</sup> Seals (RAS). The RAS system has been through several iterations over the last 10 years. Each version has provided a significant improvement over the last. The next few sections will describe the previous RAS systems.

#### 2.2.1 OTDR Only Approach

The initial approach was to use an off-the-shelf Tektronix TFP2A FiberMaster® OTDR controlled by a computer via the General Purpose Interface Bus (GPIB or IEEE-488). The TPF2A is an analog OTDR and works by injecting a short pulse of light into a fiber. Fresnel reflections occur at fiber discontinuities causing minute amounts of light to be reflected back to the transmitter. Given that the phase velocity of light in the fiber core is constant, the time of flight and the received amplitude is used to generate a waveform of reflected signal strength versus distance [3]. More details on OTDR operation will be given in Section 2.3.

In the original setup, the OTDR would repeatedly scan a loop of fiber optic cable, comparing successive scans for changes. A sudden signal drop would be perceived as a breach. The waveform would then be downloaded to a computer and compared to a predefined "secure" waveform to determine which seal was breached [2]. A fiber optic switch was present that allowed the system to scan in the both the forward and reverse directions.

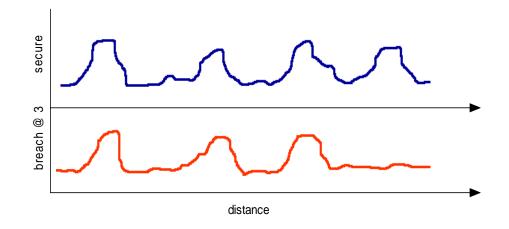

The waveform in Figure 1 illustrates an ideal case of two successive scans. The first scan (in blue) is the secure waveform. The second scan (in red) is taken some time later after connector 3 is opened. The reflection from connector 4 is no longer present because it is isolated from the system. This is an indication of a breach at seal 3.

The main problem with this approach was speed. The acquisition time for a high resolution waveform took several minutes, leaving the fiber optic seals vulnerable to undetected tampering. The system also suffered from repeatability problems. The successive OTDR scans varied in shape and peak amplitude making the design of a

Figure 1: Successive OTDR Scan Comparison

waveform comparison algorithm more difficult. Generally, clever signal processing solved the last problem but the solution was far from ideal.

#### 2.2.2 Analog Immediate Detection Unit and Tektronix OTDR

To overcome the speed issue discussed in Section 2.2.1, a new piece of hardware called the Immediate Detection Unit (IDU) was introduced that could quickly detect a fiber breach. This hardware removed the breach detection burden from the OTDR. The IDU changed the system design slightly by requiring that the seals be arranged in a loop. Light was injected into one end of the loop and verified at the opposite end. The IDU used a light emitting diode (LED) based transmitter and matched photo detector. The output of the photo detector was amplified by a potentiometer controlled analog amplifier. A binary (secure/breached) output was provided.

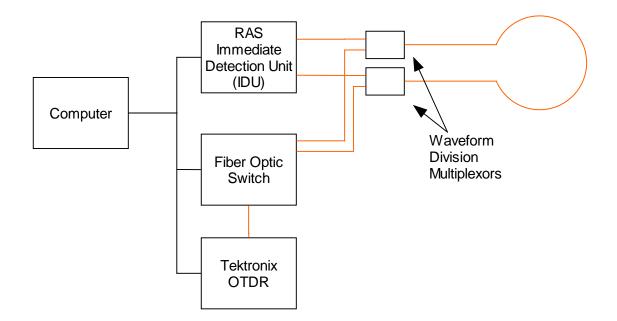

In the event of a seal breach detected by the IDU, the Tektronix TFP2A OTDR was connected to the loop (looking either forward or reverse down the loop) via a computer controlled fiber optic switch. The OTDR and IDU used two different

wavelengths, so waveform division multiplexers were used to combine the two signals onto a single fiber. The OTDR would then acquire a waveform and download it to the computer. By comparing previously acquired secure waveforms, the breach location was identified. Figure 2 is a simplified drawing of this system.

The problems with this version were limits in the seal capacity due to the signal to noise ratio (SNR), repeatability problems with the OTDR like those previously discussed and a design which made large scale deployments difficult. The analog circuitry in the IDU was temperature dependent and required setting a potentiometer for correct levels. Due to the low output power of the LED, the maximum seal count was limited to about 50 seals per loop. To monitor hundreds of items required many of these expensive setups. Furthermore, they were all isolated instruments. It was desired that all seals in a facility be monitored by a single computer.

Figure 2: Analog IDU with Tektronix OTDR

#### 2.2.3 Digital Immediate Detection Unit with Tektronix OTDR

The desire for support of large seal counts throughout a facility led to the design of the Digital Immediate Detection Unit (DIDU). The basic IDU design was leveraged and improved by using a laser diode and more sensitive receiver electronics. An added layer of security was providing by using a Field Programmable Gate Array (FPGA) to generate and verify encoded signals. Finally, an 8-bit microprocessor was added to handle communications using the Telecommunication Protocol/Internet Protocol (TCP/IP) over a standard Ethernet network.

The addition of a laser diode led to an increase in the SNR and allowed up to 150 seals to be used per loop. More importantly, since each DIDU could now be placed on a network, one computer could be used to log data and control multiple DIDUs throughout an entire facility. The DIDU also represented the first effort to miniaturize the system by using surface-mount electronics.

The main problem with the DIDU is associated with the Tektronix OTDR. By the time the DIDU was designed, Tektronix had discontinued production of the TFP2A in favor of smaller, handheld field instruments. Better OTDR performance than the TFP2A could provide had been desired for some time, and with the TFP2A no longer available there was no choice but to look for an OTDR alternative.

The DIDU also suffered from scalability issues. Each DIDU supported twenty fiber optic loops and contained an onboard switch that injected the OTDR signal into any one of them. For small deployments, the excess capacity served no functional purpose, but greatly increased system cost. The "sharing" of the OTDR between twenty loops led to an increase in the time required to locate a breach, especially in the event of multiple breaches on different loops.

#### 2.3 Optical Time Domain Reflectometer Review

The RAS system dictates somewhat unique requirements for an OTDR. The most common use of commercial OTDRs is in the telecom industry when a technician needs to locate a cut line or identify a bad splice or connector. In all of these cases, the number of connectors, splices or breaks are low and the length of fiber is high. In the RAS system, there are hundreds of connectors with only a few meters between them. Phenomena such as event dead zones and ghosting make detecting a large number of connectors separated by only a few meters a very difficult task for most commercial OTDRs. These phenomena will be discussed in the next few sections. A new approached called single photon counting optical time domain reflectometry will be introduced that solves the dead zone problem.

#### 2.3.1 Design of a basic OTDR

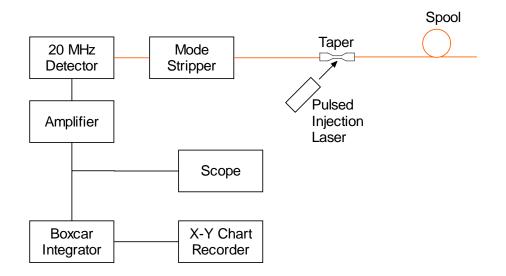

The first OTDR was conceived by Barnoski and Jensen almost 30 years ago. They were studying steady-state attenuation of fiber optic cable and realized that they could determine the attenuation coefficient by analyzing backscattered light (Rayleigh scattering). This was a great advancement because previous measurement techniques required cutting the fiber and measuring the optical power transmitted through two lengths. Barnoski and Jensen's approach led the way to testing nondestructively via one end face [3]. The setup used in their experiment is shown in Figure 3. The result most important to this work is the large reflection Barnoski and Jensen observed as a result of

Figure 3: First OTDR by Barnoski and Jensen

the cleaved end of the 360 meter spool (a reflection resulting from a feature such as a cleaved end or connector is called a Fresnel reflection). They noted that the time scale could be converted to propagation distance given a known phase velocity of light in the core. The cut end of the fiber and other discontinuities that create Fresnel reflections could therefore be located along the length of fiber optic cable.

#### 2.3.1 OTDR Dead Zones

OTDRs inject a short pulse of light into one end of a fiber and then use a highly sensitive avalanche photodiode receiver to measure the minute amount of light (typically -65 to -70 dB/m) reflected back [4]. The sensitive receivers are easily saturated by strong reflective events such as a connector or splice. The avalanche process causes a macroscopic current to flow, which lowers bias voltage. Since the photodiode has a finite capacity, some amount of time is required to recover [5]. This recovery time is known as an event dead-zone. During the dead-zone period the fiber status is unknown. The

Tektronix TFP2A has an event dead zone of 3 meters at a wavelength of 1300nm in multimode fiber. In terms of the RAS system, this dead-zone translates to a minimum required spacing between active seals. An ideal OTDR has no event dead zone.

#### 2.3.2 Analog OTDR Resolution Limits

The spatial resolution for a standard, non-gated, analog detection OTDR is limited to ~1m. This limitation is due to pulse duration and a tradeoff between fast detector response (bandwidth) and detector noise. The detector noise is proportional to the square-root of the detector bandwidth. The detector sensitivity,  $P_{\min}$ , can be expressed as

$$P_{\min} \approx NEP_{rc} \sqrt{bw/N}$$

, Equation 1

where  $NEP_{rc}$  is the noise-equivalent power of the receiver, *bw* is the bandwidth and N is the number of measurements [6].

#### 2.3.3 OTDR Ghosting

An effect called ghosting is the result of reflections that bounce between Fresnel events one or more times before reaching the receiver. The net effect is that an apparent reflection appears at some distance multiple of real events [7]. In typical RAS deployments, it is common to use the same length of fiber between container seals. When connectors occur at regular intervals, the ghost signals can overlap with real connector signals. The result is a false indication of the true reflection strength of each victim connector. Compounded ghosting becomes an even greater problem when a seal is opened, because ghosts can make a connection appear as if it is still there when in fact it has been removed from the loop. Ghosts are minimized in the RAS system by attenuating the signal, which turns out to be a requirement for the photon counting OTDR anyway (see the next section). In addition, careful signal analysis is used to help ignore the effects.

#### 2.3.4 Photon Counting OTDR

The invention of the v-OTDR is a logical progression brought about by a desire to increase dynamic range. By employing very sensitive avalanche photodiodes the receiver is able to detect a single photon. Detector availability at room temperatures is no longer a challenge; InGaAs/InP avalanche photodiode detectors cooled by Peltier coolers are readily available [8]. The challenge with designing a v-OTDR is due to the binary nature of avalanche photodiode detectors (APD). Single photon detectors operate in the Geiger mode, meaning that a single photon acts as a trigger that uses up all the stored energy in the device creating a macroscopic current that is easily detectable [5]. Therefore, the detector reacts the same whether it receives one photon or multiple photons. Since the goal of an OTDR is to provide intensity information about reflected light, a probabilistic, multi-measurement approach must be taken.

To implement the probabilistic approach successfully, light attenuation must be controlled so that during each gating period the average number of received photons is less than one [5]. Lacaita, Francese and Cova demonstrated that the SNR can be maximized by adjusting the power so that the probability of detecting a photon is 63% for each output pulse [9]. To understand the need for attenuation, consider two Fresnel reflections, A and B. Reflection A is very strong and is immediately followed by the very weak reflection B. The attenuation must be set so the stronger reflection A does not always overshadow the weaker reflection B. Once a photon is detected and the avalanche

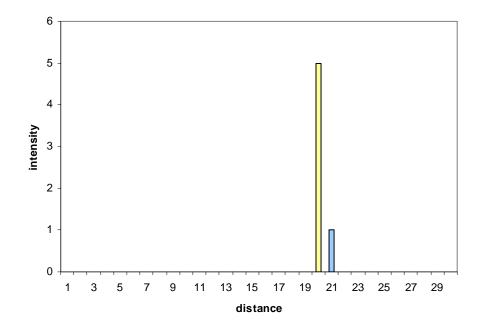

begins, there is a finite recharging time during which the detector is not sensitive. For the sake of this explanation assume that the time of flight for light in the fiber from reflection A to B is less that the APD recharge time. If we are to ever see reflection B, then the attenuation must be set such that on average a reflection does not occur from either reflection A *or* B. This will ensure that there is some probability that a reflection originates from point B. Over multiple scans, reflection probability will be "built-up" into a histogram. Table 1 and Figure 4 provide an example of how the probabilistic data is received. In this example, a photon is received for only 20% of the output pulses. Since event A at 20 meters is more intense than event B at 21 meters, 5 events are recorded from event A, while only one occurs from event B. This makes sense logically; since reflection A is stronger than B, there is a higher probability that received photons will have been generated by event A.

It should be obvious by now that in order to determine optical intensity accurately, many (thousands or tens of thousands) successive scans are required. The measured probability is proportional to incident signal power provided the detector is not saturated and the power is greater than the thermal detector noise [10 and 4]. This is both a blessing and a curse for v-OTDRs. It is a blessing in the sense that since each pulse leads to at most one detection event, there is no dead zone in the classical sense (this is ignoring multi-hit mode which will be discussed later). The lack of a classical dead zone is the primary reason for choosing to implement a v-OTDR in the RAS system. It is a curse in the sense that detection time increases because multiple scans are required. However, a multi-hit mode can be used (and is used in RAS) to decrease detection time dramatically.

| Scan Number | <b>Event Detection</b> |

|-------------|------------------------|

| Scan 1      | none                   |

| Scan 2      | none                   |

| Scan 3      | none                   |

| Scan 4      | 20                     |

| Scan 5      | none                   |

| Scan 6      | none                   |

| Scan 7      | none                   |

| Scan 8      | 20                     |

| Scan 9      | none                   |

| Scan 10     | none                   |

| Scan 11     | 21                     |

| Scan 12     | 20                     |

| Scan 13     | none                   |

| Scan 14     | none                   |

| Scan 15     | none                   |

| Scan 16     | 20                     |

| Scan 17     | none                   |

| Scan 18     | none                   |

| Scan 19     | none                   |

| Scan 20     | 20                     |

Table 1: Sample v-OTDR data for 20 scans

Figure 4: Histogram Based on Table 1

The increased dynamic range of a v-OTDR over a standard analog detection OTDR is predicted at ~7dB [6]. This leads to 2-point spatial resolution improvement of around a factor of 100 based on Equation 1. Increased spatial resolution is an obvious benefit for any system designed to locate tightly spaced fiber faults. However, as spatial resolution is increased, minimization of the pulse duration becomes critical if one is to maintain high resolution. Since a reflected photon could have come from any one of the millions of photons comprising a pulse of light, spatial resolution is limited to the pulse width. The proceeding statement assumes that the light pulse is an ideal step function. In reality, the pulse is quasi-Gaussian or may contain multiple peaks within the width. The probability of reflection is highest at the pulse peak and falls off toward the leading and trailing edges. In a real sense, the spatial resolution is less than or equal to the pulse width, which means that the design of a low cost, very short pulse (hundreds of picoseconds) laser diode driver is a vital aspect of the system. The design of such a driver is detailed in Section 4.4.

To improve the SNR further, v-OTDR implementations often gate the APD so that it is only active over a specific region of interest [11]. The starting point of the region of interest is delayed with each scan so that over successive scans the entire fiber length is analyzed. Given a constant total scan time, SNR is increased as the gating region is decreased.

A multi-hit v-OTDR shares a similarity with a gated v-OTDR in that fiber under test is virtually divided into many smaller sections. However, for a multi-hit v-OTDR, the APD is gated "on" for more than one region per output pulse. The result is that waveform acquisition speed is increased proportional to the number of active regions. This is in contrast to a single-hit gated v-OTDR in which only one backscattered pulse is measured for each output pulse. Since the RAS system needs the data as fast as possible, a multi-hit approach is used, and the region size is set to the same period as the recharge time of the avalanche photodiode detector. In the case of the Perkin-Elmer SPCM-AQR used in this design, the recharge time is 30ns. Multi-hit and gated v-OTDRs are typically more complex to design, as they require precise timing. As will be explain in the following chapters, the Event Detector and Locator employs a variant of the multi-hit approach that simplifies the design at a cost of decreased dynamic range.

### **3.0 System Design Concepts**

#### **3.1 Introduction**

This chapter aims to explore the system design from a high level. Sample system deployments will be examined and major design choices will be described. A high level functional diagram will be presented that will lay the foundation for more detailed explanations in chapters 4 and 5.

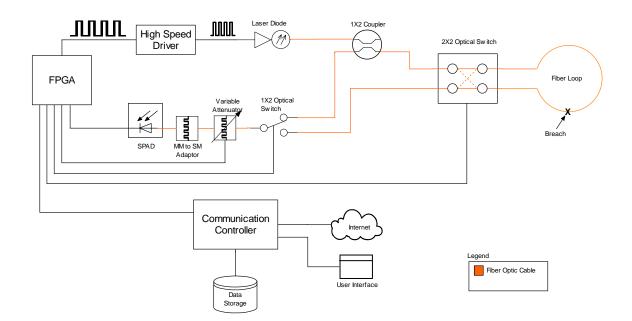

The device's primary functions are detecting an event (seal breach) and locating where that breach is. As such, the device was given the name Event Detector and Locator (EDL). This device will replace the IDU and the OTDR from previous generations of RAS systems and provide a smaller, faster, more flexible and more secure hardware architecture.

#### **3.2 Simple Deployment**

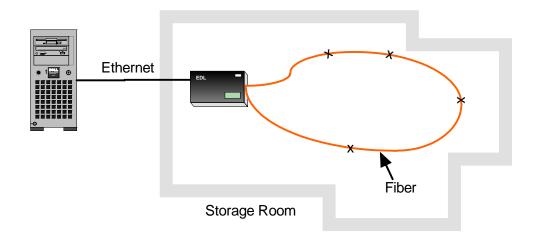

To understand the role of the EDL in the RAS system, consider Figure 5. A simple deployment is illustrated in which the EDL is connected to a single loop of fiber with multiple seals along that loop. In the event of a breach, a local visual alarm on the EDL will activate, and the computer will be notified of an unacknowledged breach. The EDL will then begin taking v-OTDR measurements in both the forward and reverse directions and will pass this data to the computer via an Ethernet connection. v-OTDR scans are taken repeatedly until the user acknowledges the breach.

Figure 5: Single Loop RAS Deployment

The direct Ethernet connection between the EDL and computer can be established with a crossover cable. While the EDL can certainly be used in this way, it is a rare case in practice and does not leverage the networking features designed into the device. The next section will discuss a more common deployment arrangement.

#### **3.3 Common Deployment**

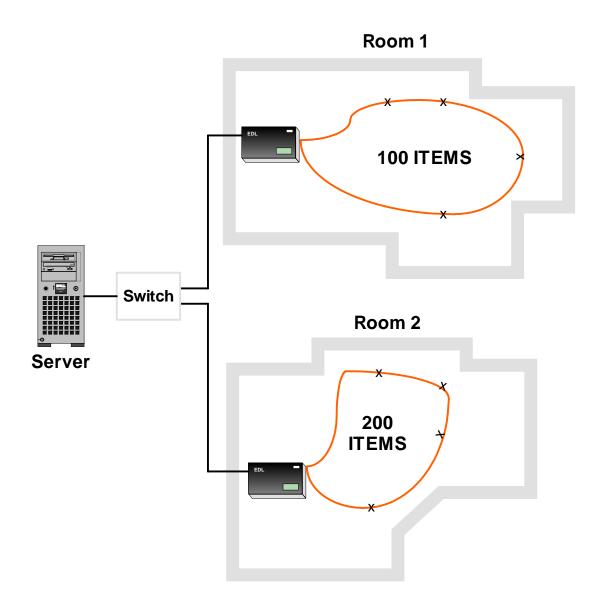

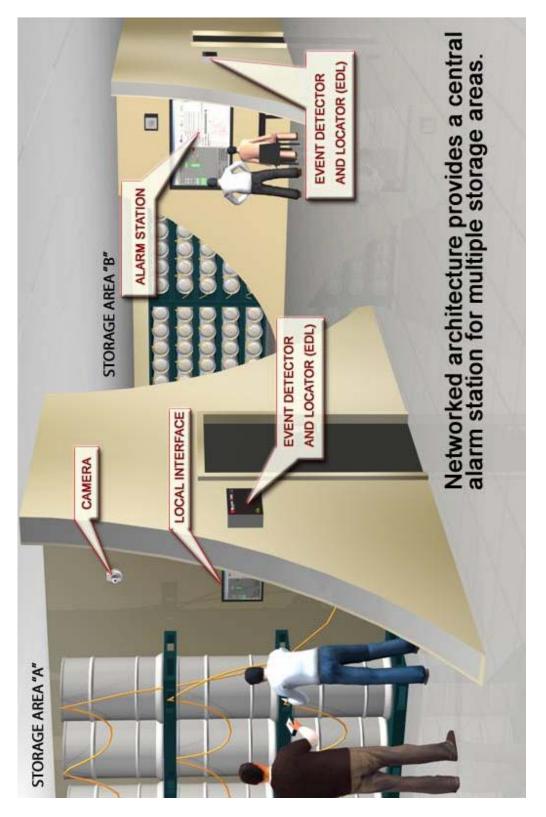

Most facilities have several rooms or vaults which often span multiple facilities. It is often desirable to monitor all RAS data in one central location. The EDL was designed as a network device that operates on existing Local Area Network (LAN) architecture or over the Internet. In either case, a group of EDL clients can communicate with a single server or host. Figure 6 and Figure 7 illustrate a more common deployment scheme.

Leveraging existing networks is a large advantage for potential deployments because it minimizes wiring and installation costs for most facilities. However, it places

Figure 6: Typical RAS Deployment

Figure 7: Typical RAS Facility Implementation

an additional burden on data security because the data is more exposed and can no longer be physically protected. To mitigate this risk, security features built into standard protocols were leveraged, including Hyper Text Transfer Protocol over Secure Socket Layer (HTTPS), the MD5 hashing algorithm and eXtensible Markup Language (XML). These tested and proven protocols greatly decreased software development time and effort by permitting the use of software libraries provided by the microprocessor core module vendor and the Microsoft .NET framework.

#### **3.4 Event Detector and Locator Theory of Operation**

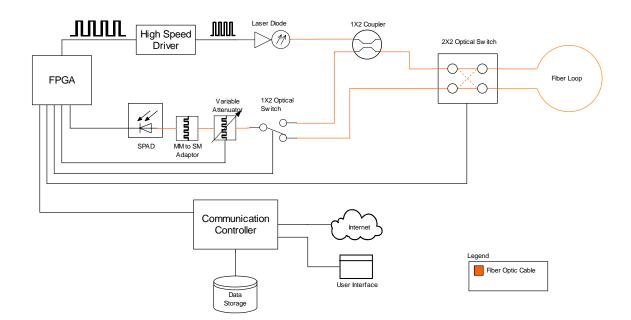

A Field Programmable Gate Array (FPGA) was chosen to implement the v-OTDR digital signal generation and timing as well as an encoding scheme for loop continuity verification. Off the shelf (OTS) equipment was used wherever possible, including an 8-bit microprocessor core module with on-board support for the Telecommunications Protocol / Internet Protocol (TCP/IP). OTS optical equipment and a modular power supply were used. Use of OTS equipment minimized the amount of custom circuit design and fabrication, which decreased development time.

Custom electronics were designed for support of the FPGA and microprocessor. Custom electronics were also designed to implement an alarm board, alarm interface and high speed laser diode driver. Firmware was developed for the FPGA and communication module in Very High Speed Integrated Circuit Hardware Description Language (VHDL) and Dynamic C. An advantage that comes with the use of an FPGA and the flexible microprocessor core module is that nearly all system functions can be modified with simple firmware changes. A major goal of this design is to incorporate event detection and event location via a v-OTDR into a single device. The EDL does just that, and it is easiest to understand the device if the reader continues to think of it as two instruments merged into one. Under normal operations, the EDL can be thought of as a simple fiber optic loop continuity checker (event detection instrument). It isn't until a breach is detected that the EDL begins to function as a v-OTDR (event location instrument). The EDL theory of operation will be explained for each mode of operation in the next sections.

#### 3.4.1 EDL in the Event Detection Mode

The diagram in Figure 8 shows the EDL in the event detection mode. The signal flow for this mode will now be discussed from a high level perspective. More specific details will be provided in the following chapters.

Starting at the FPGA, a 32-bit encoded digital word is generated and sent to the high speed laser driver. For each edge received here, a short duration (~800 picosecond) optical pulse is output from the laser diode. The light travels through a coupler which serves no purpose in this mode. From here the light goes through a 2x2 optical switch which is set in the straight through mode (this switch serves no purpose in this mode). The light then travels out of the EDL and through the fiber optic loop. Once back in the EDL (assuming the loop was not breached) the light travels through the 2x2 optical switch to the 1x2 optical switch. As indicated in Figure 8, the switch is set to allow light to pass to the variable attenuator and on to a multimode-to-singlemode adaptor. Finally, the light is sensed by the Single Photon Avalanche photodiode Detector (SPAD). The light pulse is now digitized and is input back to the FPGA where it is processed.

Figure 8: EDL Block Diagram in Event Detection Mode

#### 3.4.2 EDL in the Event Location Mode

In Figure 9 the EDL is shown in the event location (or v-OTDR) mode. In this case a TTL pulse is generated by the FPGA. The pulse is converted to a short optical pulse by the high speed driver and laser diode. The light passes through the coupler and through the 2x2 switch. The light then travels through the loop until it hits the breach. A Fresnel reflection occurs at the breach, which sends a minute amount of light back toward the transmitter. The 1x2 coupler directs some of this light to the 1x2 optical switch, through the attenuator and multimode-to-singlemode adaptor and into the SPAD. The signal is digitized by the SPAD and a signal is output to the FPGA for timing analysis.

The 2x2 switch is used for varying which end of the fiber the v-OTDR uses for measurements. Being able to change this switch provides the ability to locate a seal

Figure 9: EDL Block Diagram in Event Location Mode

breach from both ends of the fiber. It also allows determination of an open span of fiber caused by two open seals.

It is obvious that Figure 8 and Figure 9 are nearly identical. This is by design and results in a smaller, lower cost and better performing instrument. Common components are used where possible between the event detection mode and event location mode. From a hardware perspective, the 1x2 optical switch controls the EDL mode of operation.

The use of the sensitive SPAD results in a ~7dB improvement in dynamic range for the event detection part of the instrument. Because each ST style connector has an average loss of 0.2dB (varies by type and manufacturer), the net result is an increased capacity of about 35 seals per EDL over a standard photo detector based system. It should be mentioned that the signal must be heavily attenuated to avoid saturation of the SPAD, but this is not a problem as attenuators are already in place for v-OTDR operation.

### 4.0 Hardware Design

#### 4.1 Introduction

The components of the hardware design include the FPGA and support circuitry, a low cost picosecond laser driver and laser diode, an avalanche photodiode detector, an 8-bit microprocessor core module and support circuitry, alarm circuitry, power module, power filtering, a liquid crystal display and optics components including a coupler, switches and attenuator. A picture of the hardware is shown in Figure 10. In the following sections, each portion of the hardware design will be described in detail.

Figure 10: EDL Circuitry

#### **4.2 Power Circuitry**

The EDL is designed to operate from 120 volt 1 phase AC power (60 Hz). In order to save space and to minimize design time, an Astrodyne MDCA-0308 AC-DC power module was used. This module accepts input voltages from 85 VAC to 265 VAC and provides two outputs, 5 VDC @ 3A and 12 VDC @ 1.25A [12]. A supply ripple filter circuit consisting of parallel 100 $\mu$ F tantalum and 1.0 $\mu$ F ceramic capacitors is applied at each output of the power supply module.

The various components in the EDL necessitate multiple supply voltages. The FPGA requires 3.3 VDC and 1.5 VDC. The microprocessor board requires 3.3 VDC, the alarm circuitry and optics require 5 VDC, and the laser diode driver requires an isolated 5 VDC supply. To generate 3.3 VDC and 1.5 VDC for the FPGA, two LM317D2T adjustable regulators are used to step down the 5 VDC supplied from the Astrodyne power module. The laser diode driver's isolated power is generated by using an isolated dc-dc converter (NML1205). The output ripple is reduced by an L-C circuit consisting of a series inductor and parallel capacitor (relative to the input). The L-C circuit is a low-pass filter and is tuned to a cutoff frequency of about 500Hz. To isolate the laser diode driver circuit, a separate ground plane is used and is connected to the main ground plane through a high frequency noise suppressing ferrite bead.

#### **4.3 FPGA and Support Circuitry**

An Altera Stratix EP1S10F484C7 FPGA was used for this design. The FPGA is based on a 1.5V, 0.13-um process. It has 10,570 logic elements, 920,488 RAM bits, 6

phase-locked loops (PLLs) and 426 user Input/Output pins [13]. The FPGA is clocked by an external 80 MHz clock.

The Stratix FPGA was chosen based on performance, cost, the inclusion of dedicated RAM and the availability of PLLs. The included RAM allows v-OTDR data to be stored on-chip, which reduces board complexity and increases read/write speed. A PLL is used to generate several phase-shifted clocks which drive a VHDL sampler at a rate of 8 times the clock frequency. This topic will be discussed at length in Section 5.4.2.

The FPGA must be supplied with 3.3V and 1.5V for internal logic and input buffers. In addition to the use of bypass capacitors at each power entry point, Altera recommends that the board layout be customized for the power and ground pins of each PLL. Since the PLL circuits contain analog components embedded in a digital device, the power pins are isolated to improve noise immunity [14]. To maintain this isolation several board layout recommendations are provided by Altera. The chosen method was a thick power trace from the power supply to each PLL power pin. Each power pin is decoupled with a  $0.1\mu$ F and a  $0.001\mu$ F parallel combination of ceramic capacitors.

A reset switch is included in the design. This switch connects an FPGA pin to ground when pressed. The switch is useful for debugging and is not used during normal operation of the instrument.

An Altera EPC8 contains 8Mbit of flash memory used to store the configuration data for the FPGA. At power-on, the EPC8 is configured to automatically load the configuration data to the FPGA. The EPC8 supports the Joint Test Action Group (JTAG) interface which enables in-system programmability (ISP) of the flash memory [15]. This feature provides the ability to reprogram the FPGA in the field with a notebook computer. An appropriate connector is included on the main circuit board to support ISP.

#### 4.4 Low Cost Picosecond Laser Driver

As mentioned in Section 2.3.4, minimizing the laser pulse duration is critical to maintaining high spatial resolution measurements. After an exhaustive vendor search, the only viable solution was the id300 offered by ID Quantique in Switzerland. The id300 produces 300 picosecond pulses but is cost prohibitive. The RAS system can meet defined specifications with pulses up to 1.5ns full width half maximum (FWHM). This requirement stems from the fact that the phase delay based sampler on the FPGA (to be discussed later) has a maximum sampling rate of 8 times the clock frequency. At a clock frequency of 80 MHz, the sampling rate is 640 MHz or once every 1.56 nanoseconds. Spatial resolution of the v-OTDR is therefore constrained by the sampling rate as long as the laser pulse duration is kept below 1.56 nanoseconds.

The ratio of speed of light in a vacuum to the speed of light in a material is called the index of refraction. The Corning multimode fiber used for RAS has an effective group index of refraction of 1.496 at 850nm [16]. The phase velocity, v, of light in the fiber is inversely proportional to the refractive index as shown in Equation 2, where c is the speed of light and n is the group index of refraction [17]. Light therefore travels about 67% as fast in the fiber as it does in a vacuum. 1.56 nanoseconds equates to 0.31 meters in the fiber. If the laser pulse is kept below 1.56 nanoseconds then the resolution of the v-OTDR will be 0.31 meters or about a foot.

$$v = \frac{c}{n}$$

Equation 2

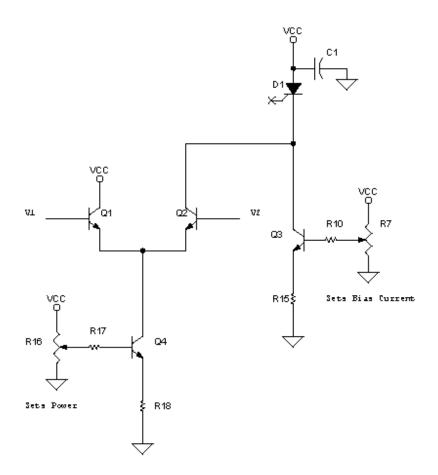

To meet the cost requirement while still supplying pulse widths of ~800ps meant that a custom laser driver was necessary. The basic design concept is taken from a current switch circuit that is commonly used in emitter-coupled logic (ECL) gates. This core section of the laser diode driver is shown in Figure 11. The collector current differences in terms of the base-emitter voltages can be expressed as

$$i_{C1} - i_{C2} = \alpha_F I_{EE} \tanh\left(\frac{\upsilon_{BE1} - \upsilon_{BE2}}{2V_T}\right) [18].$$

Equation 3

Equation 3 reveals that a small change in the base-emitter voltage of Q1 with respect to Q2 or of Q2 with respect to Q1 causes nearly all of the current to switch from one transistor to the other. More importantly, both transistors are held in the forward-active region at all times. The "off" transistor flows a small current at all times and can switch rapidly into high conduction when its base-emitter voltage rises just a few tenths of a volt over the paired transistor. The saturation region is therefore avoided, allowing current to switch between the two transistors at sub-nanosecond speeds.

In Figure 11, the Q1 side of the switch is normally flowing. When the voltage at V2 increases so that V2>V1 by more than a few tenths of a volt, then current will flow though Q2. The amplitude of the current flowing through the switch (Q1 or Q2) is set by the current source composed of Q4, R17, R18 and R16. The current source is variable based on the setting of potentiometer R16. Another current source composed of Q3, R15, R10 and R7 provides a constant bias current to the laser diode D1. It was expected that the diode would switch faster if biased just under its minimum lasing current. In practice, the bias current does not increase switching speed but does cause the laser diode to output

Figure 11: ECL Based Core of Picosecond Diode Driver

steady low-level light which increases noise in the system. The bias current is set to zero in the final design.

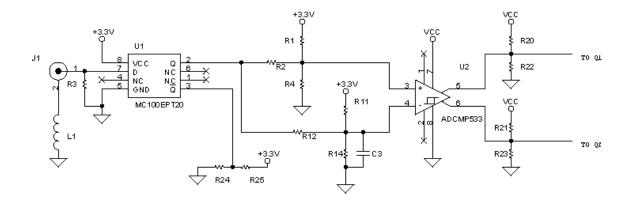

The next design challenge was to generate the switching voltages at the inputs of Q1 and Q2. The inputs to Q1 and Q2 must be at ECL voltage levels and have pulse widths of ~800ps. In order for the transistors to remain in the forward-active region, they must be held at a voltage above breakdown and switched around that voltage. An easy way to meet the ECL requirements was to drive the current switch with an ECL device. The input stage is shown in Figure 12.

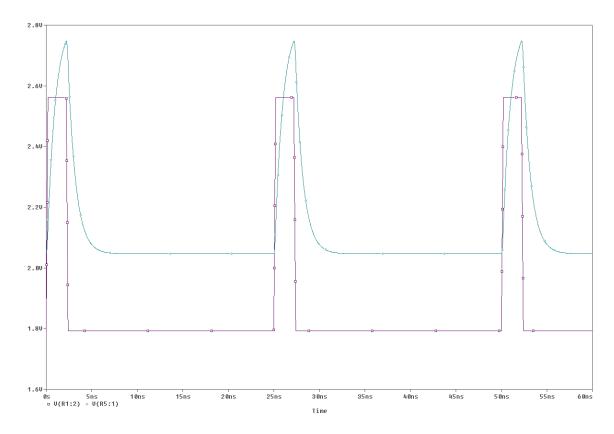

The circuit works by accepting a transistor-transistor logic (TTL) level pulse sourced from the FPGA and converting it to positive emitter-coupled (PECL) levels. One side of the PECL signal, Q, is then split it into two signals while the other side ( $\overline{Q}$ ) is terminated and not used. The top side of the split signal is biased by R1 and R4 to be at a lower voltage than the bottom side which is biased by R11 and R14. Under quiescent state the input to the comparator at the negative terminal is greater than the positive terminal. This translates into Q1 being active in the quiescent state as expected. When a pulse is received, the response at the negative input of the comparator lags that of the positive input because of the time it takes to charge C3. This effect is shown in Figure 13. During the lag, the signal at the positive side of the comparator (in purple) becomes greater than the signal at the negative terminal (in teal). Hence a very short PECL pulse is output from the comparator for each incoming pulse. The length of the pulse is proportional to the value of C3 (larger = longer pulse). It does not matter how long the TTL input pulse is, but duty cycle must be such that the capacitor has time to discharge.

Figure 12: Input Stage of Picosecond Diode Driver

Figure 13: Picosecond Driver Delayed Pulse Response

The PECL outputs of the comparator are terminated and directly feed transistors Q1 and Q2 in the current mirror.

The resulting circuit cost less than \$20 in parts and consumes only 2.38 square inches of printed circuit board real estate. The value of C3 was chosen so that 800ps FWHM optical pulses are generated. The waveform in Figure 14 shows the optical pulse acquired using a Thor Labs SV2 photo detector and a 1 GHz oscilloscope.

The driver fails to work at pulse widths shorter than about 650ps. It is assumed that this limitation is due to differential input voltage converging to near zero as the delay caused by smaller values of C3 gets shorter. This can be visualized as the teal waveform becoming more similar in shape to the purple waveform in Figure 13. This is not a surprise as the comparator switching performance declines as the input voltage difference decreases [19].

## 4.5 Control and Communication Module

Control and communication for the EDL is handled by a Rabbit Semiconductor RCM3360 core module. This module (shown in Figure 15) contains a Rabbit 3000 8-bit microprocessor running at 44 MHz, a 10/100Base-T Ethernet chip, 512KB flash, 512KB program Static Random Access Memory (SRAM), 512KB data SRAM and support for an extreme digital (also know as xD, a memory card format used by Olympus and Fuji) memory card up to 128 MB. The module features 52 digital input/output ports and 6 serial ports [20].

Figure 14: Picosecond Driver Optical Output Pulse

Figure 15: Rabbit RCM3360 Core Module

The RCM3360 includes a development environment called Dynamic C which integrates code editing, compiling, linking, loading and debugging of the Rabbit 3000 processor into one package. Dynamic C follows ANSI C standards but adds several enhancements that help develop embedded applications [21]. These enhancements are listed below (taken from the Dynamic C user manual).

- Function chaining allows segments of code to be embedded within one or more functions.

- Costatements allow concurrent parallel processes to be simulated (much like multithreading).

- Cofunctions allow cooperative processes to be simulated in a single program.

- Slice statements allow preemptive processes in a single program.

- Dynamic C supports embedded assembly code and stand-alone assembly code.

- Dynamic C Has *shared* and *protected* keywords that help protect data shared between different contexts or stored in battery-backed memory.

- Dynamic C supports features that allow the programmer to make fullest use of extended memory.

The RCM3360 is a plug in module that requires 3.3 VDC to operate. The programming port is self contained on the module. The main board contains a reset switch wired to the reset pin on the RCM3360. This switch is useful for debugging and restarting code execution during testing but is not used in normal operation. The main board also contains a 3.3 VDC battery that is wired to the RCM3360 to maintain the real-time clock and provide data backup. Should the EDL lose power, the battery is used to preserve variables stored in flash memory. For example, breach acknowledgement state variables are held in battery-backed memory so the state remains after a power cycle.

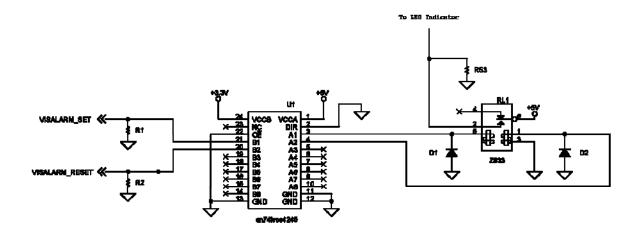

#### 4.6 Alarm Circuitry

The EDL contains a visual alarm that flashes in the event of an unexpected seal breach. The alarm output comes from the RCM3360 module and through a SN74LVCC4245 bus transceiver which converts to voltage levels from 3.3 VDC to 5 VDC. The outputs of the bus transceiver toggle a latching relay. This relay controls a 5 VDC signal to the light emitting diode (LED) indicator board. The relay circuit is shown in Figure 16. A latching relay is used to ensure that the alarm state remains set until it is acknowledged by a user, even if the power is cycled.

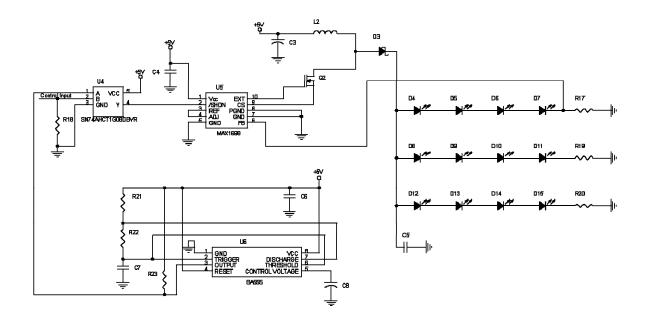

The output of the latching relay drives the LED indicator circuit in Figure 17. This circuit has a 555 timer running in the astable multivibrator mode driving one input of an AND gate. When the control input signal is high, the output of the AND gate follows the astable multivibrator output. The frequency of the astable multivibrator is given by:

$$f = \frac{1.44}{(R_{21} + 2R_{22})C_7}$$

[22]. Equation 4

The output of the AND gate drives the shutdown pin of a MAX1698 highefficiency step-up current regulator. Under non-alarm conditions the current regulator is held in shutdown mode. During an alarm condition the current regulator is continuously cycled between on and shutdown which causes the LED array to flash. The high intensity surface mount white LEDs are arranged in a tight 4x3 cluster.

Figure 16: Alarm Interface Circuitry

Figure 17: EDL Light Emitting Diode Circuit

# **4.7 Optical Components**

The optical components used in the design are commercially available off-theshelf items. The fiber optic cable used in the RAS system is 62.5/125 micron multimode fiber (62.5 micron core, 125 micron glass cladding). Multimode fiber receives its name due to a core that is much larger than the wavelength of transmitted light. The large core allows multiple optic pathways. In typical applications, multiple wavelengths (modes) are used in the same fiber. Multimode fiber was originally used because the connections are generally higher loss (cause large Fresnel reflections) and are therefore easier to see with an OTDR [23]. Today, multimode fiber is used mainly because of legacy equipment (i.e. the ability to retrofit older installations with new hardware without replacing fiber). Each optical component is described in the following sections.

# 4.7.1 Laser Diode

The laser diode is manufactured by PD-LD Inc., part number PL85R001ST73-T-O. It operates at 850nm with a minimum fiber coupled power of 1mW. The threshold current is 30mA. The diode is soldered directly to a circuit board and is coupled to 62.5/125 multimode fiber via an ST style connector.

## 4.7.2 1x2 Coupler

The 1x2 coupler is manufactured by Gould Fiber optics, part number 15-21200-50-1212. The role of the coupler is to direct backscattered light to the receiver when the EDL is in v-OTDR mode. The coupler is non-directional, meaning that light entering any node will be distributed evenly between the other two nodes. The coupler is supplied with three six inch 62.5/125 multimode fiber pigtails with ST connectors.

# 4.7.3 Optical Switches

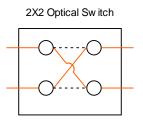

A 1x2 optical switch and a 2x2 optical switch from Agiltron are used. Both switches are controlled with a simple 5 VDC interface. The 1x2 switch (part number LB-12011316) is normally set so the EDL is in the event detection mode (see Figure 8). The switch changes state when 5 VDC is applied. The switch is non-latching and reverts when voltage is removed. The 2x2 switch (part number LB-22011316) is normally set to the pass through mode, which sets up the v-OTDR for a forward direction scan as in Figure 8 and Figure 9. When a reverse direction scan is requested, 5 VDC is applied, changing the optical path to that of Figure 18. The optical switches have a cycle time of less than 10ms and are rated for 10 million cycles.

#### 4.7.4 Dicon Fiber Optic Variable Attenuator

As previously mentioned, both the v-OTDR and event detector require careful attenuation. Attenuation characteristics of the fiber under test are based on fiber length, number of connections (seals) and quality of connector couplings. Since these factors are unknown for a newly setup EDL, a variable attenuator is required to adjust the receiver sensitivity to match the fiber under test. The Dicon NAT500-8-62-ST attenuator has a

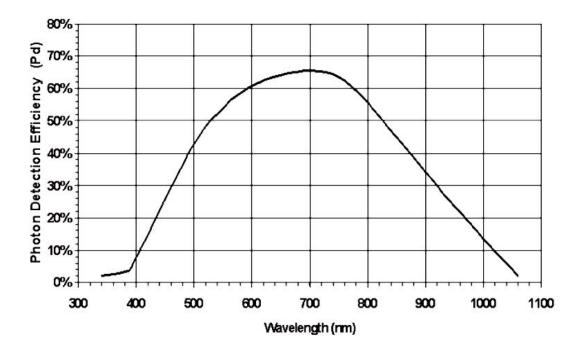

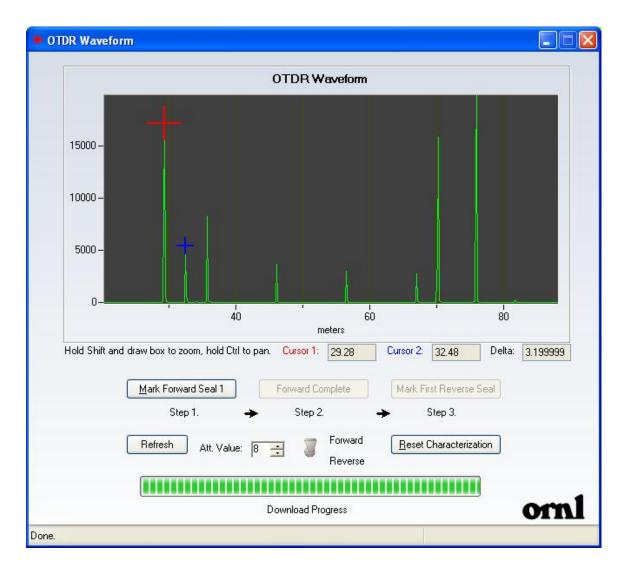

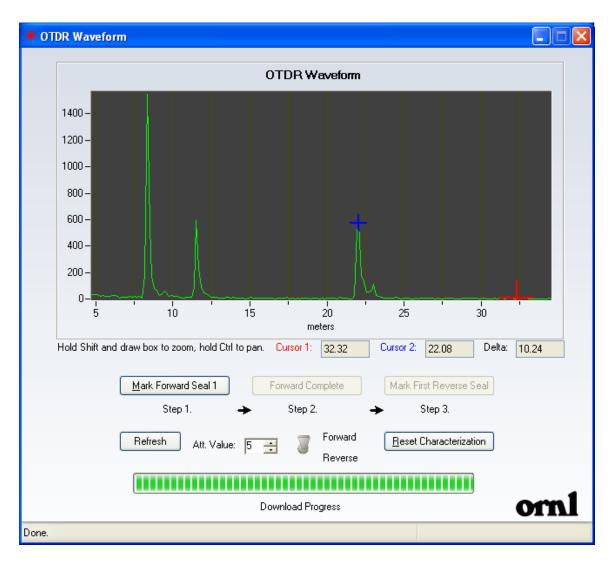

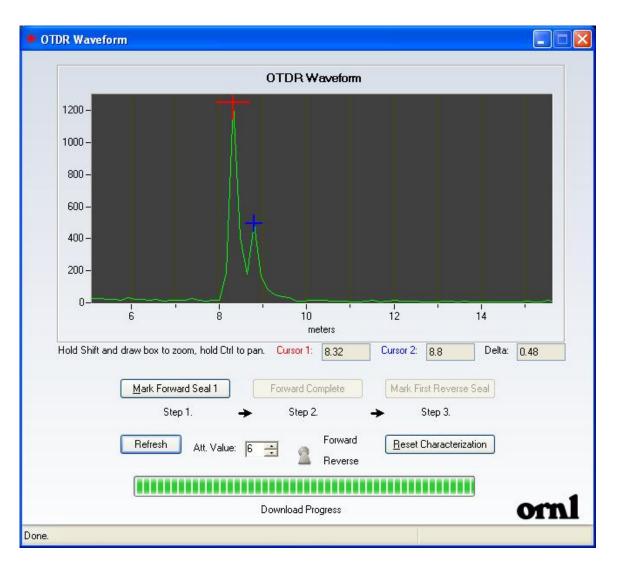

Figure 18: 2x2 Optical Switch in Reverse Mode